# Octal, 13-Bit Voltage-Output DAC with Parallel Interface

AD7838

#### **FEATURES**

Eight 13-Bit DACs in One Package

Full 13-Bit Performance without Adjustments

Buffered Voltage Outputs

Offset Adjust for Each DAC Pair

±5 V Supply Operation

Unipolar or Bipolar Output Swing to ±4.5 V

Output Settling to 1/2 LSB in 5 μs

Double Buffered Digital Inputs

Microprocessor and TTL/CMOS Compatible

Asynchronous Load Facility using LDAC Inputs

Clear Function to User-Defined Voltage

Power-On-Reset, Outputs Power Up at DUTGND

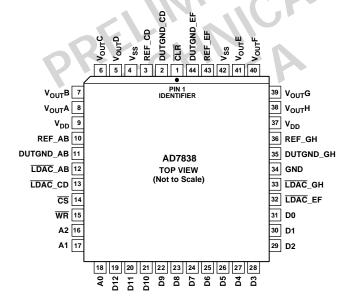

44-Lead PLCC Package

Pin Compatible with MAX547

#### **APPLICATIONS**

Process Control

Automatic Test Equipment

General Purpose Instrumentation

Digital Offset and Gain Adjustment

Arbitrary Function Generators

Avionics Equipment

#### GENERAL DESCRIPTION

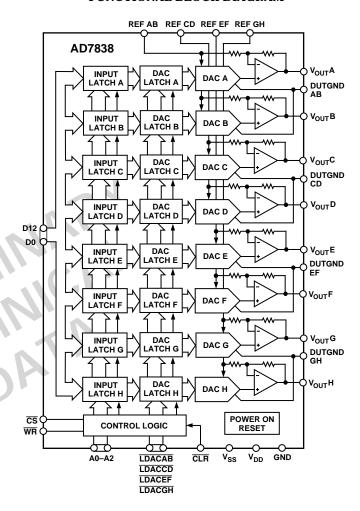

The AD7838 contains eight 13-bit, voltage-output digital-to-analog converters (DACs). The output voltages are provided through on-chip precision output amplifiers into which an external offset voltage can be inserted via the DUTGND pins. The AD7838 operates from a  $\pm 5~V \pm 5\%$  supply. Bipolar output voltages with up to  $\pm 4.5~V$  voltage swing can be achieved with no external components. The AD7838 has four separate reference inputs; each is connected to two DACs, providing different scale output voltages for every DAC pair.

The AD7838 features double-buffered interface logic with a 13-bit parallel data bus. Each DAC has an input latch and a DAC latch. Data in the DAC latch sets the output voltage. The eight input latches are addressed with three address lines. Data is loaded to the input latch with a single write instruction. An asynchronous  $\overline{LDAC}$  input transfers data from the input latch to the DAC latch. The four  $\overline{LDAC}$  inputs each control two DACs, and all DAC latches can be updated simultaneously by asserting

#### **FUNCTIONAL BLOCK DIAGRAM**

all  $\overline{LDAC}$  pins. An asynchronous clear input resets the output of all eight DACs to the relevant DUTGND. Asserting  $\overline{CLR}$  resets both the DAC and the input latch to bipolar zero (1000 Hex). On power-up, reset circuitry performs the same function as  $\overline{CLR}$ . All logic inputs are TTL/CMOS compatible.

The AD7838 is available in a 44-lead PLCC package.

## AD7838-SPECIFICATIONS

(V<sub>DD</sub> = +5 V; V<sub>SS</sub> = -5 V; DUTGNDXX = GND = 0 V; R<sub>L</sub> =10 k $\Omega$  and C<sub>L</sub> = 50 pF to GND, T<sub>A</sub><sup>1</sup> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| Parameter                                           | В                     | Units    | Test Conditions/Comments                                  |  |

|-----------------------------------------------------|-----------------------|----------|-----------------------------------------------------------|--|

| ACCURACY<br>Resolution                              | 13                    | Bits     |                                                           |  |

| Relative Accuracy                                   | ±2                    | LSB max  | Typically ±0.5 LSB                                        |  |

| Differential Nonlinearity                           | ±1                    | LSB max  | Guaranteed Monotonic Over Temperature                     |  |

| Bipolar Zero-Code Error                             | ±20                   | LSB max  | Typically ±5 LSB                                          |  |

| Gain Error                                          | ±8                    | LSB max  | Typically ±1 LSB                                          |  |

| V <sub>DD</sub> Power Supply Rejection <sup>2</sup> | $\pm 0.0025$          | %/% max  | $\Delta \hat{	ext{Gain}}/\Delta \hat{	ext{V}}_{	ext{DD}}$ |  |

| V <sub>SS</sub> Power Supply Rejection <sup>2</sup> | $\pm 0.0025$          | %/% max  | $\Delta Gain/\Delta V_{SS}$                               |  |

| Load Regulation                                     | 0.3                   | LSB typ  | $R_L = Unloaded to 10 k\Omega$                            |  |

| REFERENCE INPUTS <sup>3, 4</sup>                    |                       |          |                                                           |  |

| Input Range                                         | DUTGND                | V min    |                                                           |  |

|                                                     | $V_{\mathrm{DD}}$     | V max    |                                                           |  |

| Input Impedance                                     | 5                     | kΩ min   |                                                           |  |

| OUTPUT CHARACTERISTICS                              |                       |          |                                                           |  |

| Maximum Output Voltage                              | V <sub>DD</sub> - 0.5 | V max    |                                                           |  |

| Minimum Output Voltage                              | $V_{SS} + 0.5$        | V min    |                                                           |  |

| DYNAMIC PERFORMANCE                                 |                       |          | . 1                                                       |  |

| Voltage Output Slew Rate                            | 3                     | V/μs typ |                                                           |  |

| Output Settling Time                                | 5                     | μs typ T | Settling to 0.5 LSB of Full Scale <sup>5</sup>            |  |

| Digital Feedthrough                                 | 5                     | nV-s typ |                                                           |  |

| Digital Crosstalk                                   | 5                     | nV-s typ |                                                           |  |

| DIGITAL INPUTS                                      |                       |          |                                                           |  |

| V <sub>INH</sub> , Input High Voltage               | 2.4                   | V min    |                                                           |  |

| V <sub>INL</sub> , Input Low Voltage                | 0.8                   | V max    |                                                           |  |

| I <sub>INH</sub> , Input Current                    | ±1                    | μA max   | $V_{IN} = 0 \text{ V or } V_{DD}$                         |  |

| C <sub>IN</sub> , Input Capacitance <sup>6</sup>    | 10                    | pF max   |                                                           |  |

| POWER REQUIREMENTS                                  |                       |          |                                                           |  |

| $V_{ m DD}$                                         | 5                     | V nom    | ±5% for Specified Performance                             |  |

| $ m V_{SS}$                                         | -5                    | V nom    | ±5% for Specified Performance                             |  |

| $I_{ m DD}$                                         | 44                    | mA max   | Typically 14 mA                                           |  |

| $I_{SS}$                                            | 40                    | mA max   | Typically 11 mA                                           |  |

REV. 0 -2-

NOTES

<sup>1</sup>Temperature Range for B Version: -40°C to +85°C.

<sup>&</sup>lt;sup>2</sup>PSRR is tested by changing the respective supply voltage by  $\pm 5\%$ .

$<sup>^3</sup>$ For best performance, REFxx should be greater than DUTGNDxx by 2 V and less than  $V_{DD}$  – 0.6 V. The device operates with reference inputs outside this range, but performance may degrade.

<sup>4</sup>Reference input resistance is code dependent.

$<sup>^5\</sup>text{Typical}$  settling time with 1000 pF capacitive load is 10  $\mu s.$

<sup>&</sup>lt;sup>6</sup>Guaranteed by design, not production tested.

Specifications subject to change without notice.

##

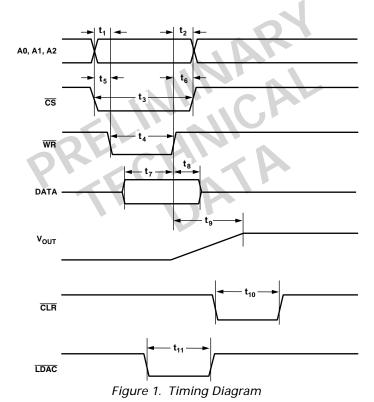

| Parameter       | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Units                            | Description                                                |  |  |

|-----------------|----------------------------------------------|----------------------------------|------------------------------------------------------------|--|--|

| $t_1$           | 10                                           | ns min Address Valid to WR Setup |                                                            |  |  |

| $t_2$           | 0                                            | ns min                           |                                                            |  |  |

| $t_3$           | 50                                           | ns min                           | CS Pulse Width                                             |  |  |

| $t_4$           | 50                                           | ns min                           | WR Pulse Width                                             |  |  |

| $t_5$           | 0                                            | ns min                           | CS to WR Setup Time                                        |  |  |

| $t_6$           | 0                                            | ns min                           | $\overline{\text{CS}}$ to $\overline{\text{WR}}$ Hold Time |  |  |

| $t_7$           | 50                                           | ns min                           | Data Valid to WR Setup Time                                |  |  |

| t <sub>8</sub>  | 0                                            | ns min                           | Data Valid to WR Hold Time                                 |  |  |

| $t_9$           | 5                                            | μs typ                           | Output Settling Time                                       |  |  |

| t <sub>10</sub> | 100                                          | ns min                           | CLR Pulse Width                                            |  |  |

| t <sub>11</sub> | 50                                           | ns min                           | LDAC Pulse Width                                           |  |  |

#### NOTES

Specifications subject to change without notice.

REV. 0 -3-

$<sup>^{1}</sup>All$  input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V. Timing applies for all grades of the part.

<sup>&</sup>lt;sup>2</sup>Rise and fall times should be no longer than 50 ns.

### AD7838

#### ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

| $(T_A = +25^{\circ}C \text{ unless otherwise no})$ | eted)                                       |

|----------------------------------------------------|---------------------------------------------|

| V <sub>DD</sub> to GND                             | 0.3 V to +6 V                               |

| $V_{SS}$ to GND                                    | +0.3 V to -6 V                              |

| Digital Inputs to GND .                            | 0.3 V to V <sub>DD</sub> +0.3 V             |

| REFxx                                              | $\dots$ DUTGND – 0.3 to $V_{DD}$ +0.3       |

| DUTGNDxx                                           | $\dots \dots V_{SS}$ – 0.3 to $V_{DD}$ +0.3 |

| $V_{\rm OUT}$                                      | $V_{DD}$ to $V_{SS}$                        |

| Max Current Into REFxx                             | Pin ±10 mA                                  |

| Max Current Into Any Otl                           | her Signal Pin ±50 mA                       |

| Operating Temperature Ra                           | ange                                        |

| Industrial (B Version)                             | 40°C to +85°C                               |

| Storage Temperature Range       | -65°C to +150°C |

|---------------------------------|-----------------|

| Junction Temperature            | +150°C          |

| PLCC Package, Power Dissipation | TBD mW          |

| $\theta_{JA}$ Thermal Impedance | 48°C/W          |

| Lead Temperature, Soldering     |                 |

| Vapor Phase (60 sec)            | +215°C          |

| Infrared (15 sec)               | +220°C          |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model    | Temperature<br>Range | Relative<br>Accuracy<br>(LSBs) | DNL<br>(LSBs) | Package<br>Description             | Package<br>Option |

|----------|----------------------|--------------------------------|---------------|------------------------------------|-------------------|

| AD7838BP | −40°C to +85°C       | ±2                             | ±1            | Plastic Leaded Chip Carrier (PLCC) | P-44A             |

#### PIN CONFIGURATION

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7838 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4- REV. 0

<sup>&</sup>lt;sup>2</sup>Transient currents of up to 100 mA will not cause SCR latchup.